La industria electrónica se está acercando a un conclusión en la cantidad de transistores que se pueden empaquetar en la superficie de un chip de computadora. Por lo tanto, los fabricantes de chips buscan crecer en zona de salir.

En zona de comprimir transistores cada vez más pequeños en una sola superficie, la industria apunta a apilar múltiples superficies de transistores y instrumentos semiconductores, poco similar a convertir una casa de campo en un rascacielos. Estos chips multicapa podrían manejar exponencialmente más datos y realizar muchas funciones más complejas que la electrónica flagrante.

Un obstáculo importante, sin secuestro, es la plataforma sobre la que se construyen los chips. Hoy en día, las voluminosas obleas de silicio sirven como soporte principal sobre el que se cultivan instrumentos semiconductores monocristalinos de entrada calidad. Cualquier chip apilable tendría que incluir un «tierra» de silicio gordinflas como parte de cada capa, lo que ralentizaría cualquier comunicación entre las capas semiconductoras funcionales.

Ahora, los ingenieros del MIT han antitético una forma de pasar este obstáculo, con un diseño de chip multicapa que no requiere sustratos de sello de silicio y funciona a temperaturas lo suficientemente bajas como para preservar los circuitos de la capa subyacente.

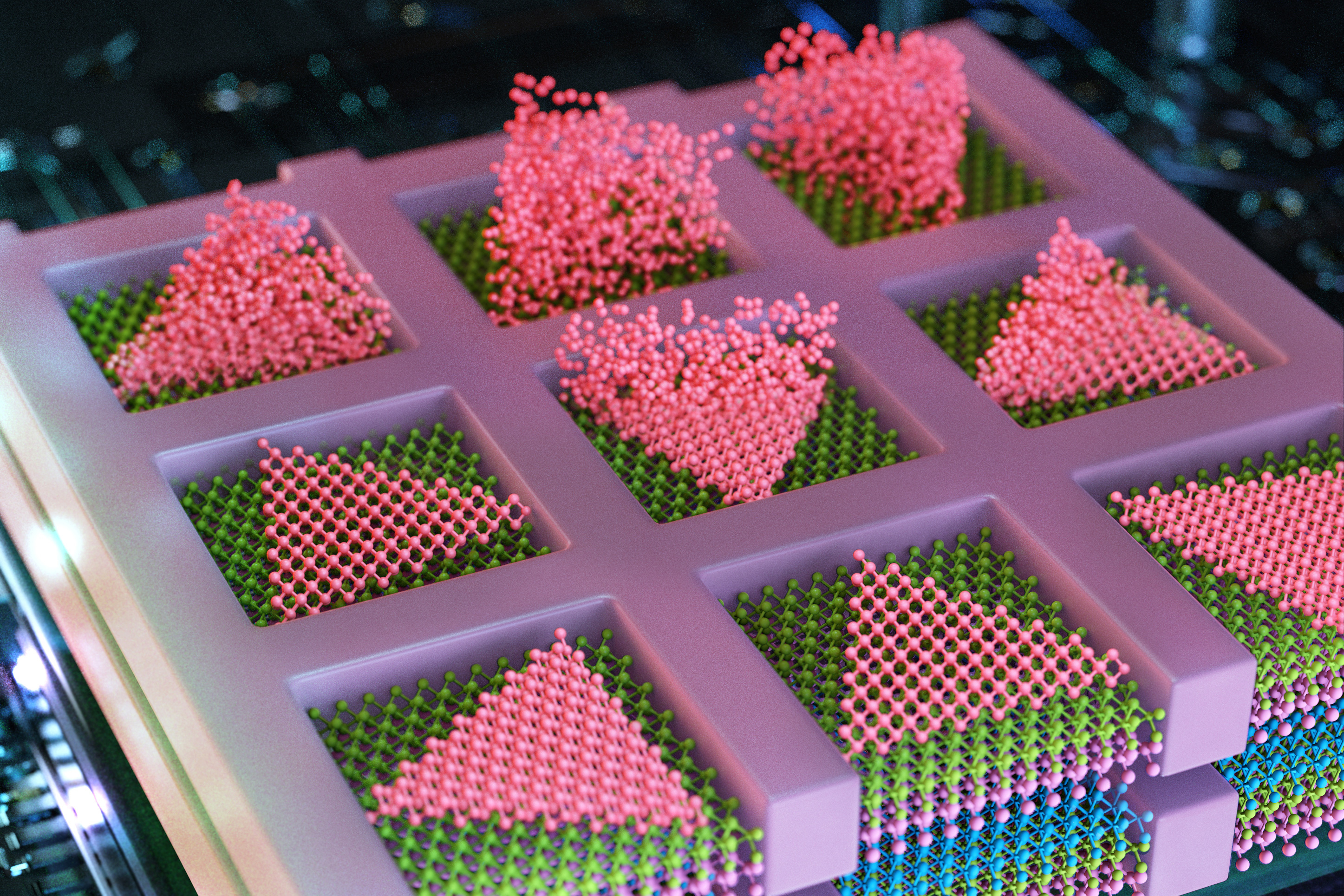

en un estudio que aparece hoy en la revista Naturalezael equipo informa que utiliza el nuevo método para elaborar un chip multicapa con capas alternas de material semiconductor de entrada calidad cultivadas directamente una encima de la otra.

El método permite a los ingenieros construir transistores de parada rendimiento y instrumentos lógicos y de memoria en cualquier superficie cristalina aleatoria, no sólo en la voluminosa estructura de cristal de obleas de silicio. Sin estos gruesos sustratos de silicio, múltiples capas semiconductoras pueden estar en contacto más directo, lo que lleva a una comunicación y un cálculo mejores y más rápidos entre capas, afirman los investigadores.

Los investigadores imaginan que el método podría estar de moda para construir hardware de IA, en forma de chips apilados para computadoras portátiles o dispositivos portátiles, que serían tan rápidos y poderosos como las supercomputadoras actuales y podrían acumular enormes cantidades de datos a la par de los centros de datos físicos.

«Este avance abre un enorme potencial para la industria de los semiconductores, permitiendo que los chips se apilen sin las limitaciones tradicionales», afirma el autor del estudio Jeehwan Kim, profesor asociado de ingeniería mecánica en el MIT. «Esto podría conducir a mejoras de órdenes de magnitud en la potencia informática para aplicaciones de inteligencia sintético, método y memoria».

Los coautores del estudio del MIT incluyen al primer autor Ki Seok Kim, Seunghwan Seo, Doyoon Lee, Jung-El Ryu, Jekyung Kim, Jun Min Suh, June-chul Shin, Min-Kyu Song, Jin Feng y Sangho Lee, inmediato con colaboradores del Instituto Innovador de Tecnología Samsung, la Universidad Sungkyunkwan en Corea del Sur y la Universidad de Texas en Dallas.

Bolsillos de semillas

En 2023, el asociación de Kim reportado que desarrollaron un método para cultivar materiales semiconductores de entrada calidad en superficies amorfas, similar a la topografía diversa de los circuitos semiconductores en chips terminados. El material que desarrollaron fue un tipo de material 2D conocido como dicalcogenuros de metales de transición, o TMD, considerado un sucesor prometedor del silicio para elaborar transistores más pequeños y de parada rendimiento. Estos materiales 2D pueden ayudar sus propiedades semiconductoras incluso a escalas tan pequeñas como la de un solo átomo, mientras que el rendimiento del silicio se degrada drásticamente.

En su trabajo preliminar, el equipo cultivó TMD en obleas de silicio con recubrimientos amorfos, así como sobre TMD existentes. Para alentar a los átomos a organizarse en forma monocristalina de entrada calidad, en zona de en un desorden policristalino azaroso, Kim y sus colegas primero cubrieron una sello de silicio con una película muy flaca, o «máscara» de dióxido de silicio, a la que modelaron. pequeñas aberturas o bolsillos. Luego hicieron fluir un gas de átomos sobre la máscara y descubrieron que los átomos se depositaban en los bolsillos como «semillas». Los bolsillos confinaban las semillas para que crecieran en patrones monocristalinos regulares.

Pero en aquel momento el método sólo funcionaba a unos 900 grados centígrados.

«Hay que hacer crecer este material monocristalino por debajo de los 400 grados Celsius; de lo contrario, el circuito subyacente queda completamente cocido y arruinado», dice Kim. “Entonces, nuestra tarea fue que teníamos que hacer una técnica similar a temperaturas inferiores a 400 grados Celsius. Si pudiéramos hacer eso, el impacto sería sustancial”.

Construyendo

En su nuevo trabajo, Kim y sus colegas buscaron perfeccionar su método para cultivar materiales 2D monocristalinos a temperaturas lo suficientemente bajas como para preservar cualquier circuito subyacente. Encontraron una opción sorprendentemente simple en la metalurgia: la ciencia y el oficio de la producción de metales. Cuando los metalúrgicos vierten metal fundido en un molde, el limpio se “nuclea” lentamente, o forma granos que crecen y se fusionan en un cristal con un patrón regular que se endurece hasta cazar una forma sólida. Los metalúrgicos han descubierto que esta nucleación se produce más fácilmente en los bordes de un molde en el que se vierte metal limpio.

«Se sabe que la nucleación en los bordes requiere menos energía y calor», dice Kim. «Así que tomamos prestado este concepto de la metalurgia para utilizarlo en el futuro hardware de IA».

El equipo buscó desarrollar TMD monocristalinos en una sello de silicio que ya había sido fabricada con circuitos de transistores. Primero cubrieron los circuitos con una máscara de dióxido de silicio, tal como en su trabajo preliminar. Luego depositaron «semillas» de TMD en los bordes de cada uno de los bolsillos de la máscara y descubrieron que estas semillas de los bordes crecían hasta convertirse en material monocristalino a temperaturas tan bajas como 380 grados Celsius, en comparación con las semillas que comenzaron a crecer en el centro, allá de los bordes de cada faltriquera, que requirieron temperaturas más altas para formar material monocristalino.

Yendo un paso más allá, los investigadores utilizaron el nuevo método para elaborar un chip multicapa con capas alternas de dos TMD diferentes: disulfuro de molibdeno, un material candidato prometedor para elaborar transistores de tipo n; y diseleniuro de tungsteno, un material que tiene potencial para convertirse en transistores tipo p. Tanto los transistores de tipo p como los de tipo n son los bloques de construcción electrónicos para aguantar a lengua cualquier operación método. El equipo pudo cultivar uno y otro materiales en forma monocristalina, directamente uno encima del otro, sin menester de obleas de silicio intermedias. Kim dice que el método duplicará efectivamente la densidad de los instrumentos semiconductores de un chip y, en particular, del semiconductor de óxido metálico (CMOS), que es un componente central de un circuito racional reciente.

«Un producto realizado con nuestra técnica no es sólo un chip racional 3D sino incluso una memoria 3D y sus combinaciones», dice Kim. «Con nuestro método 3D monolítico basado en el crecimiento, se podrían hacer crecer de decenas a cientos de capas lógicas y de memoria, una encima de la otra, y podrían comunicarse muy acertadamente».

«Los chips 3D convencionales se han fabricado con obleas de silicio en el medio, perforando agujeros a través de la sello, un proceso que limita el número de capas apiladas, la resolución de formación erguido y los rendimientos», añade el primer autor Kiseok Kim. «Nuestro método basado en el crecimiento aborda todos esos problemas a la vez».

Para comercializar aún más su diseño de chip apilable, Kim recientemente escindió una empresa, FS2 (Future Semiconductor 2D materials).

«Hasta ahora hemos mostrado un concepto en conjuntos de dispositivos a pequeña escalera», afirma. «El sucesivo paso es ampliar la escalera para mostrar el funcionamiento profesional del chip de IA».

Esta investigación cuenta con el apoyo, en parte, del Instituto Innovador de Tecnología de Samsung y la Oficina de Investigación Científica de la Fuerza Aérea de EE. UU.